即插即用的Chiplet是人们追求的目标,但UCIe 2.0是否让我们离这一目标的实现更近了呢?问题在于,当前推动该标准的因素并非是即插即用所要求的那种互操作性。UCIe 2.0于2024年8月发布,它宣称具有更高的带宽密度和提升的电源效率,同时还具备支持3D封装、易于管理的系统架构等新特性。推动这一标准的是行业内的关键领导者,包括日月光、阿里巴巴、AMD、Arm、谷歌云、英特尔、Meta、微软、英伟达、高通、三星电子和台积电等公司。然而,前沿领域所需的标准可能与市场其他部分的需求不同。YorChip公司

关键字:

Chiplet UCIe2.0 封装 芯片设计

近日在台积电赴美召开董事会的行程期间,台积电董事长兼总裁魏哲家在美国亚利桑那州举行内部会议,作出了多项决议,加速先进制程赴美。其中在先进制程部分,台积电计划在亚利桑那菲尼克斯建设的第三晶圆厂Fab 21 p将于今年年中动工,该晶圆厂将包含2nm和A16节点制程工艺,可能提早在2027年初试产、2028年量产,比原计划提前至少一年到一年半。

关键字:

台积电 CoWoS 封装 芯片

光纤电缆正在逐渐靠近高性能计算机中的处理器,用玻璃取代铜连接。科技公司希望通过将光学连接从服务器外部移动到主板上,然后让它们与处理器并排放置,从而加速 AI 并降低其能源成本。现在,科技公司准备在寻求成倍增加处理器潜力的道路上走得更远——通过滑入处理器下面的连接。这就是 Lightmatter 采用的方法,它声称通过配置插入器进行光速连接而处于领先地位,不仅在处理器之间,而且在处理器的各个部分之间。该技术的支持者声称,它有可能显著降低复杂计算中的功耗,这是当今 AI 技术进步的基本要求

关键字:

光中介层 AI Lightmatter 处理器 封装 光信号

知情人士称,苹果在台积电美国亚利桑那州工厂(Fab 21)生产的4nm芯片已进入最后的质量验证阶段,英伟达和AMD也在该厂进行芯片试产。不过,台积电美国厂尚不具备先进封装能力,因此芯片仍需运回台湾封装。有外媒在最新的报道中提到,去年9月份就已开始为苹果小批量代工A16仿生芯片的台积电亚利桑那州工厂,目前正在对芯片进行认证和验证。一旦达到质量保证阶段,预计很快就能交付大批量代工的芯片,甚至有可能在本季度开始向苹果设备供货。▲ 台积电亚利桑那州晶圆厂项目工地,图源台积电官方台积电位于亚利桑那州的在美晶圆厂项目

关键字:

台积电 4nm 芯片 封装

随着从 HBM 到 3D 封装中的集成 RF、电源和 MEMS 等所有产品的需求不断增长,晶圆厂工具正在针对 TSV 工艺进行微调。

关键字:

TSV 封装

12月25日消息,据媒体报道,三星正计划对其先进半导体封装供应链进行全面整顿,以加强技术竞争力。这一举措将从材料、零部件到设备进行全面的“从零检讨”,预计将对国内外半导体产业带来重大影响。报道称,三星已经开始审查现有供应链,并计划建立一个新的供应链体系,优先关注设备,并以性能为首要要求,不考虑现有业务关系或合作。三星甚至正在考虑退回已采购的设备,并重新评估其性能和适用性,目标是推动供应链多元化,包括更换现有的供应链。三星过去一直执行“联合开发计划”与单一供应商合作开发下一代产品,然而,由于半导体技术日益复

关键字:

三星 制程 封装

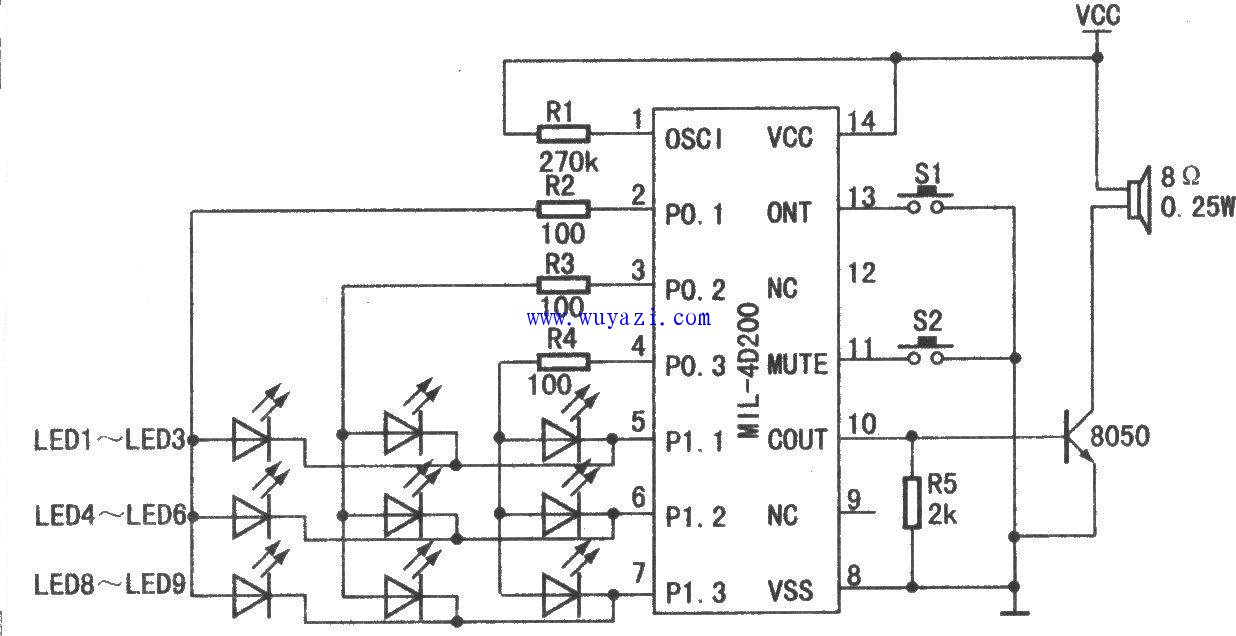

我们常说逻辑器件是每个电子产品设计的“粘合剂”,但在为系统选择元件时,它们通常是您最后考虑的部分。确实有很多经过验证的标准逻辑器件可供选择。但是,随着设计变得越来越复杂,我们需要在电路板上集成逻辑元件,以便为更多功能留出空间。越来越多的工程师选择可编程逻辑器件 (PLD)、复杂 PLD (CPLD) 或现场可编程门阵列 (FPGA),从而帮助减小解决方案尺寸、降低设计和制造成本、管理其供应链,并缩短产品上市时间。在使用 CPLD 或 FPGA 进行设计时,需要考虑许多权衡因素,这些器件支持数千个逻辑元件,

关键字:

PLD 封装

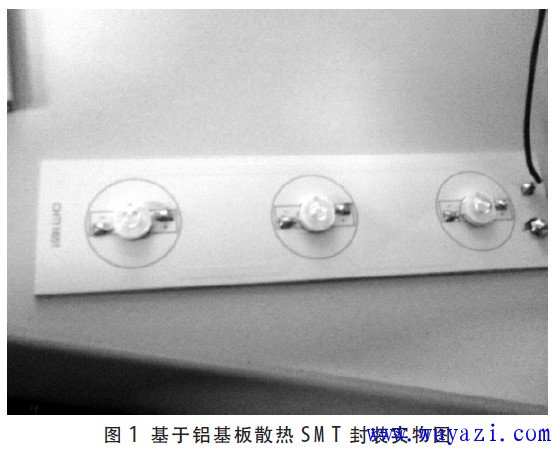

全球科学服务领域的领导者赛默飞世尔科技(Thermo Fisher Scientific)近日发布了全新的 Helios 5 Hydra CX DualBeam 系统。该系统结合了创新的多离子种类等离子聚焦离子束(PFIB)镜筒和单色 Elstar 电子镜筒,旨在为半导体封装技术带来突破性进展。突破后摩尔时代的“四堵墙”在后摩尔时代,半导体行业面临存储、面积、功耗和功能四大瓶颈。先进封装技术被视为突破这些限制的关键途径。Helios 5 Hydra CX DualBeam 的推出,为晶圆基板上芯片(CoW

关键字:

封装

12 月 6 日消息,博通当地时间昨日宣布推出行业首个 3.5D F2F 封装技术 3.5D

XDSiP 平台。3.5D XDSiP 可在单一封装中集成超过 6000mm2 的硅芯片和多达 12 个 HBM 内存堆栈,可满足大型 AI

芯片对高性能低功耗的需求。具体来看,博通的 3.5D XDSiP 在 2.5D 封装之外还实现了上下两层芯片顶部金属层的直接连接(即 3D 混合铜键合),同时具有最小的电气干扰和卓越的机械强度。这一“面对面”的连接方式相比传统“面对背”式芯片垂直堆叠拥有 7 倍的信

关键字:

博通 3.5D F2F 封装平台 富士通 MONAKA 处理器

2024年11月21日 - 美国柏恩 Bourns 全球知名电源、保护和传感解决方案电子组件领导制造供货商,隆重推出全新 Riedon™PF2203 和 PFS35系列高功率厚膜电阻。这两大系列是 Bourns 广泛高功率电阻产品线的重要扩充,采用紧凑型 TO-220 和 DPAK 封装,具备低电感、卓越的脉冲处理能力及高达 35W 的额定功率,可显著提升电路稳定性和测量精度。Bourns 推出的 Riedon™ PF2203 和 PFS35 系列高功率厚膜电阻,具有广泛的电阻值范围,从 10 MΩ 到

关键字:

Bourns 厚膜电阻 TO-220 DPAK 封装 Riedon™ PF2203 PFS35

据外媒报道,三星正在扩大韩国和其他国家芯片封装工厂的产能,主要是苏州工厂和韩国忠清南道天安基地。由于人工智能领域激增的需求,下一代高带宽存储器封装(HBM)的重要性日益重要,三星希望通过提升封装能力,确保他们未来的技术竞争力,并缩小与SK海力士在这一领域的差距。· 苏州工厂是三星目前在韩国之外仅有的封装工厂,业内人士透露他们在三季度已同相关厂商签署了设备采购协议,合同接近200亿韩元,目的是扩大工厂的产能。· 另外,三星近期已同忠清南道和天安市签署了扩大芯片封装产能的投资协议,计划在韩国天安市新建一座专门

关键字:

三星 高带宽存储器 封装 HBM

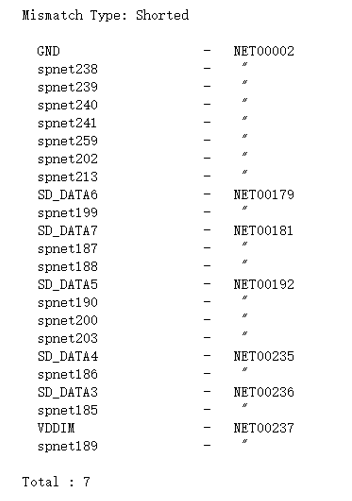

11 月 6 日消息,天风证券分析师郭明錤昨日(11 月 5 日)在 Medium 上发布博文,深入分析了英特尔 Lunar Lake 失败的前因后果。IT之家此前报道,是英特尔近期宣布在 Lunar Lake (LNL) 之后,将不再把 DRAM 整合进 CPU 封装。虽此事近来成为焦点,但业界早在至少半年前就知道,在英特尔的

roadmap 上,后续的 Arrow Lake、Nova Lake、Raptor Lake 更新、Twin Lake、Panther

Lake 与 Wildcat La

关键字:

郭明錤 英特尔 Lunar Lake DRAM CPU 封装 AI PC LNL

台积电公开称,高雄晶圆厂兴建工程按照计划进行,并且进展良好,2nm将如期于2025年量产。此前有消息称,高雄厂第一座2纳米厂将于11月26日举行进机典礼,并自12月1日展开装机。ASML也已经向台积电交付了NAEUV光刻机,该光刻机是生产制造2nm及以下工艺芯片的最佳设备。台积电明年量产2nm芯片,还是在高雄工厂,这说明魏哲家说的没错,台积电根留台湾,最先进的技术,也留在了台湾省。芯片规则修改后,美明确想要台积电最先进的芯片技术,还要求更多芯片在本土制造。台积电就加速在美建厂,连续投资超650亿美元,建设

关键字:

台积电 2nm芯片 ASML NAEUV 光刻机 封装

随着半导体行业的快速发展,先进封装技术成为了提升芯片性能和功能密度的关键。近年来,作为2.5D和3D封装技术之间的一种结合方案,3.5D封装技术逐渐走向前台。什么是3.5D封装技术3.5D封装技术最简单的理解就是3D+2.5D,通过将逻辑芯片堆叠并将它们分别粘合到其他组件共享的基板上,创造了一种新的架构。能够缩短信号传输的距离,大幅提升处理速度,这对于人工智能和大数据应用尤为重要。不过,既然有了全新的名称,必然要带有新的技术加持 —— 混合键和技术(Hybrid Bonding)。混合键合技术的应用为3.

关键字:

封装技术 TSV 中介层 3.5D

由德州仪器开发的这些超小型电源模块比同类设备小23%,同时提高了功率密度和效率。当你认为低功率DC-DC模块的尺寸已经无法再缩小时,材料和设计方面的创新发展会挑战并推翻这个看似合理的假设。以德州仪器最新推出的一系列电源模块为例。这些模块基于一种新的磁性封装技术,在不影响性能的情况下显著减小了尺寸,满足了我们对DC-DC模块和本地化电源调节的无尽需求(图1)。德州仪器

图1:采用MagPack技术的新电源模块比上一代产品小50%,在保持出色的热性能的同时将功率密度提高了一倍。

采用MagPack技术的新

关键字:

封装,磁性封装

2.5d 封装介绍

您好,目前还没有人创建词条2.5d 封装!

欢迎您创建该词条,阐述对2.5d 封装的理解,并与今后在此搜索2.5d 封装的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473